Kosten, Qualität und Durchsatz sind wesentliche Faktoren für eine erfolgreiche Fertigung in der Halbleiterindustrie. Durch die wachsende Akzeptanz neuer Arten von Wafersubstraten, dünneren Wafern und das Skalieren auf kleinere Dimensionen sowie Substrate mit größeren Abmessungen entwickelt sich das Wafer-Dicing zu einem kritischen Wertschöpfungsprozess, der nicht nur die Erträge von Halbleiterbauelementen sicherstellt, sondern auch steigert.

Gleichzeitig wird die Funktionalität der Mikroelektronik-Bauteile bei gleichbleibendem oder geringerem Platzbedarf stetig erweitert. Infolgedessen wenden sich die Chiphersteller dem vertikalen Stacking und heterogenen Integrationsschemata zu, um kleinere Bauelemente mit höherer Leistung fertigen zu können. Daraus resultiert ein steigender Bedarf an Verfahren zur selektiven Bearbeitung von funktionellen Oberflächen, ohne die darunterliegenden Schichten und Strukturen zu beeinträchtigen.

Für Leistungshalbleiter aus Siliziumkarbid (SiC), sogenannte Power-Devices, wurde bisher das thermische Annealing zur Bildung des ohmschem Kontakts (OCF) auf der Rückseite der SiC-Wafern verwendet, um deren elektrischen Eigenschaften sowie die mechanische Festigkeit zu verbessern.

Um die elektrische Leistung und das Wärmemanagement von SiC-Anwendungen zu verbessern, werden jedoch immer dünnere SiC-Wafer benötigt. Diese Entwicklung führt dazu, dass die Hitzeeinwirkungen der beim thermischen Annealing gängigen Produktionsverfahren zu einer Gefährdung für die bereits auf der Wafer-Vorderseite integrierten Aktiv-Komponenten werden.

Thermisches Annealing wird auch für die Produktion von Sensor-Elementen verwendet, die auf den Effekten des Riesenmagento-Widerstand (englisch: Giant magnetoresistance, kurz: GMR) und dem Magnetischen Tunnelwiderstand (englisch: Tunnel Magnetoresistance, kurz: TMR) basieren. Bei traditionellen thermischen Annealing-Verfahren werden allerdings mehrere Produktionsschritte benötigt, um z. B. Sensoren mit unterschiedlichen magnetischen Ausrichtungen zu produziere. Insbesondere wenn verschiedene Ausrichtungen auf Multi-Chip-Packages realisiert oder integrierte, monolithische Chip-Pakete in einem Prozess verarbeitet werden sollen, erfordert dies bisher viele einzelne zeitintensive Produktionsschritte.

Zur Reduzierung der Prozess-Schritt-Anzahl sind neue Ansätze gefragt: Selektives Laser-Annealing kann die Anzahl der Prozessschritte im Vergleich signifikant verringern und den gesamten Produktionsprozess damit vereinfachen. Außerdem ermöglicht es die wesentlich kostengünstigere Produktion von integrierten monolithischen Sensor-Paketen.

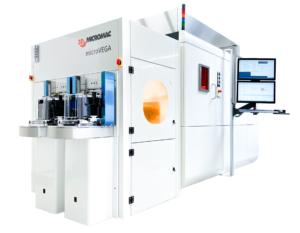

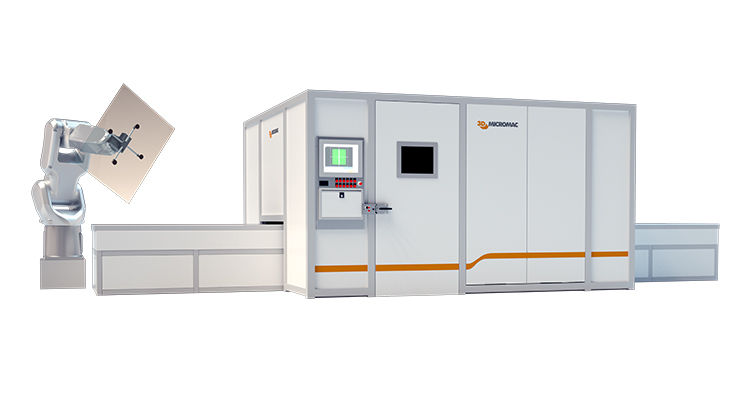

3D-Micromac erfüllt die kritischen Anforderungen der Halbleiter-Industrie sowohl mit dem microDICE-Laser-Mikrobearbeitungssystem, welches die TLS-Dicing-Technologie (Thermisches Laserstrahl Separieren) zum Trennen der Wafer verwendet, als auch mit dem microPRO XS-System für das selektive Laserannealing im Bereich OCF und dem microVEGA xMR-System für das selektive Laser-Annealing im Bereich der Magnetfeld-Sensoren-Fertigung.